Home Search Collections Journals About Contact us My IOPscience

Smart-Cut: A New Silicon On Insulator Material Technology Based on Hydrogen Implantation and Wafer Bonding \*1

This content has been downloaded from IOPscience. Please scroll down to see the full text.

1997 Jpn. J. Appl. Phys. 36 1636

(http://iopscience.iop.org/1347-4065/36/3S/1636)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 128.111.121.42

This content was downloaded on 13/07/2015 at 16:05

Please note that terms and conditions apply.

# Smart-Cut: A New Silicon On Insulator Material Technology Based on Hydrogen Implantation and Wafer Bonding\*

Michel Bruel, Bernard Aspar and Andre-Jacques Auberton-Hervé<sup>1</sup>

$LETI/CEA\ D\'{e}partement\ de\ Microtechnologies,\ CEA\ Grenoble-17\ rue\ des\ Martyrs-38054\ Grenoble\ Cedex\ 9,\ France\ ^1SOITEC,\ Site\ Technologique\ ASTEC-15\ rue\ des\ Martyrs-38054\ Grenoble\ Cedex\ 9,\ France$

(Received September 6, 1996; accepted for publication November 28, 1996)

An alternative route to existing silicon on insulator (SOI) material technologies such as SIMOX (separation by implanted oxygen) and BESOI (bonded and etch-back SOI) is the new Smart-Cut process, which appears to be a good candidate to achieve ULSI criteria. The Smart-Cut process involves two technologies: wafer bonding and ion implantation associated with a temperature treatment which induces a in-depth splitting of the implanted wafer. The details of the Smart-Cut process, the physical phenomena involved in the different technological steps such as hydrogen implantation related mechanisms and wafer bonding are discussed. The characteristics of the final structure in terms of thickness homogeneity, crystalline defects, surface microroughness, and electrical characterization are presented. Other applications of this process are also highlighted.

KEYWORDS: silicon on insulator, wafer-bonding, smart-cut, hydrogen implantation

#### 1. Introduction

Up to now silicon on insulator (SOI) technology developments were mainly geared to radiation-hardened electronics for military and space applications. Today, SOI technologies appear to be a key issue for low-power, low-voltage electronics, and should play a major role in future ULSI developments.<sup>1)</sup> One of the key issues for development of SOI-based microelectronics is the availability of good-quality, low-cost SOI material in suitable quantity. Among the many SOI material technologies developed during the past two decades, SIMOX (separation by implanted oxygen) has reached the level where industrial companies are able to offer standard specified products on the market, and for the past few years there has been a growing interest in SOI material technology based on wafer bonding and etch back (BESOI).<sup>2,3)</sup> For achieving thin uniform SOI layers the BESOI technology involves either an etch stop layer or a combination of accurate thickness mapping and fine local thinning with a localized plasma. 4,5) In addition to these processes the new Smart-Cut SOI process involves the best features of the implantation and wafer bonding technologies for production of Unibond<sup>6)</sup> wafers. Implantation enables a high degree of uniformity of the top silicon layer to be obtained whereas the wafer bonding step enables the good crystal quality of the silicon wafer to be preserved. This process, taking advantage of its unique splitting effect, appears to be an alternative route, able to meet the criteria necessary for development of ULSI technologies: thickness homogeneity, good crystalline quality, low cost, and availability.

The Smart-Cut process<sup>7,8)</sup> basically comprises four main steps (Fig. 1):

—Step 1: Hydrogen implantation into a wafer A capped with a dielectric layer, thermally grown  $\mathrm{SiO}_2$  for example (dose in the  $3.5 \times 10^{16}$  to  $1 \times 10^{17}$  cm<sup>-2</sup> range)

—Step 2: Hydrophilic bonding at room temperature of wafer A to a handle wafer B (wafer B is either bare or capped). Both wafers are previously cleaned using

Fig. 1. Principle of the Smart-Cut process.

a modified RCA process. Wafer B plays a key role in the Smart-Cut process as a stiffener and provides the bulk silicon under the buried oxide in the SOI structure.

—Step 3: Two-phase heat treatment of the two bonded wafers. During the first phase (400–600°C) the implanted wafer A splits into two parts: a thin layer of monocrystalline silicon remaining bonded to wafer B thus giving rise to a SOI structure, and the remainder of wafer A. The second high temperature treatment phase (around 1100°C) strengthens the chemical bonds.

—Step 4: Touch polishing-after splitting, the layer of the SOI structure exhibits micro-roughness which makes polishing of the surface necessary for elimination of the disturbed region.

<sup>1</sup> Si wafer-B Si wafer-A **Bonding** Si wafer-A interface 2 Defect and Si wafer-B microcavity zone Si wafer-A Surface microroughness SOI wafer 4 SOI wafer Si wafer-A

<sup>\*</sup>Smart Cut is a registered trademark of SOITEC.

Noteworthy: Wafer A whose surface layers (Si+SiO<sub>2</sub>) have been removed by the splitting process can be recycled using touch polishing to be used as wafer B in a subsequent process flow.

#### 2. Hydrogen Implantation and Splitting

High dose inert gas or hydrogen implantation in materials can induce visible macroscopic effects such as blistering, swelling, flaking and exfoliation. These effects have been known for a long time.<sup>9, 10)</sup> This is a major issue for design of thermonuclear reactors where extensive damage to the inner wall of the reactor occurs due to helium ion bombardment.<sup>11)</sup>

The possibility of making silicon flakes using hydrogen or inert gas ion implantation into silicon opens up the way for a new SOI material technology. The challenge involves increasing the flake area by a factor of about  $10^8$  ( $100 \, \mu \text{m}^2$  to full wafer), keeping the crystalline structure of the layer defect-free (especially preventing the layer from being subjected to stresses leading to plastic deformation).

Due to the small amount of damage induced by implanted hydrogen ions (most of the stopping power is due to inelastic scattering), the relatively moderate ion fluences, and self-annealing of defects during implantation, it appears that silicon flakes originating from single-crystal silicon can be prevented from undergoing irreversible damage.

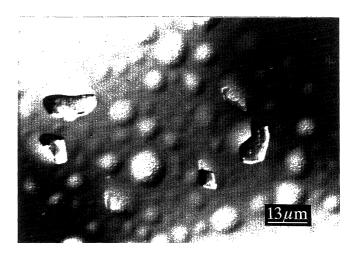

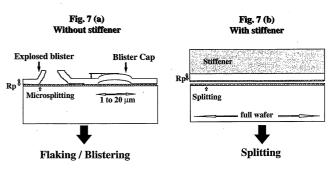

For silicon, blistering and flaking (Fig. 2) can be obtained in two ways:

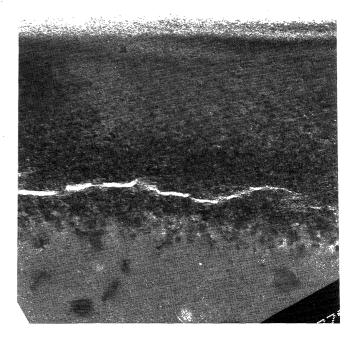

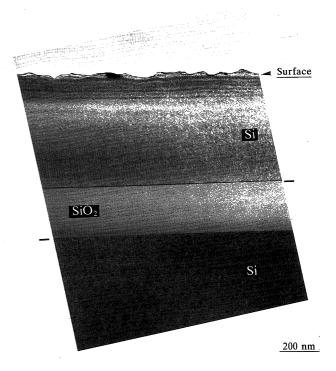

—Firstly: by performing high-dose implantation. In this case blistering becomes visible for doses of around  $2\times10^{17}~\rm cm^{-2}$ , and flaking occurs as the dose is increased. —Secondly: by performing medium-dose implantation and annealing. The first step consists of achieving limited hydrogen dose implantation (around  $3\times10^{16}~\rm cm^{-2}$  to  $1\times10^{17}~\rm cm^{-2}$ ). The second step consists of performing a thermal treatment (400°C to 600°C) resulting in blistering and flaking. These effects are associated with in-depth microscopic defects. Transmission electron microscopy (XTEM) cross sections show microsplits extending parallel to the surface (Fig. 3). It is noteworthy that the surface quality after step one is sufficient to enable bonding of the implanted surface to another wafer.

The originality of the Smart-Cut process is to use the basic physical phenomenon related to blistering, i.e. creation of microcavities containing a gas phase, as a way of inducing in-depth splitting at the end of the range of implanted protons over the whole wafer.

In the Smart-Cut process, the handle wafer is bonded to the implanted wafer and acts both as a stiffener and as a support for the transferred layer. Stiffening of the upper layer must be understood as attaching it to a substrate or layer with appropriate mechanical properties. This can be achieved by deposition of thick and adherent layers on the surface or by bonding of a substrate to the surface.

As the need for very flat surfaces is a key issue in wafer bonding techniques, the possibility of keeping the surface free from any deformation or even blisters after the im-

Fig. 2. Blistering and flaking at the silicon surface.

Fig. 3. TEM cross section of a crack in silicon after hydrogen implantation and annealing.

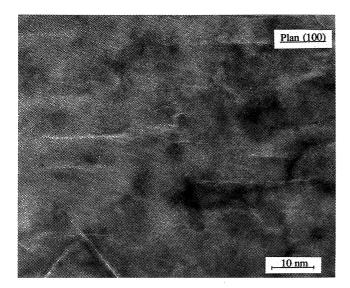

plantation step appears to be of prime importance. It is in the medium dose implantation case in which no defects are observed at the surface whereas some microscopic defects are present in the silicon. High-resolution XTEM observations of as-implanted samples show microcavities located at a depth corresponding to the projected range, oriented following the (111) and (100) planes for (100) silicon wafers (Fig. 4).

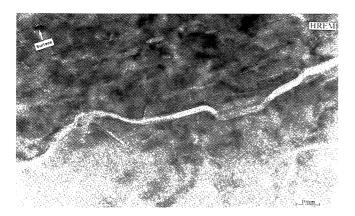

The mean size of the microcavities increases during annealing (Fig. 5) leading to the formation of a crack parallel to the bonded surface. This crack propagates along the large microcavities which are distributed within a layer whose thickness is about  $\Delta R_{\rm p}$  (projected range straggling). So after splitting, a high degree of surface microroughness is obtained (12 nm RMS) (Fig. 6).

To summarize, medium dose hydrogen implantation into silicon induces microsplitting during annealing at a depth corresponding to peak hydrogen concentration.

Fig. 4. High resolution TEM cross section of microcavities on hydrogen-implanted silicon.

Fig. 5. High resolution TEM cross section of microcavities on hydrogen-implanted silicon after low-temperature annealing.

However, this microsplitting develops differently depending on the conditions at the wafer surface; i.e. (Fig. 7),—if the surface is free (without stiffener), during annealing the microsplitting induces deformation of the thin

ing the microsplitting induces deformation of the thin film and blisters appear at the surface.

—if a stiffener is present on the surface, deformation of the thin film is impossible and the microsplitting induces splitting of the full wafer.

## 3. Cleaning and Bonding

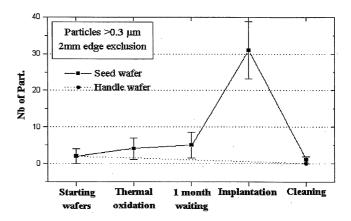

For achieving high-quality bonding, the contacting wafers must be scratch-free and cleaned to remove any particle or organic contamination. Microroughness also influences the bonding and must be lower than 0.5 nm RMS.<sup>12)</sup> For formation of the SOI wafer, hydrophilic conditions are used to bond the implanted oxidized wafer to the silicon handle substrate. The Smart-Cut process requires specific cleaning conditions before bonding because the implantation step modifies the oxide surface in terms of particle and organic contamination. The particle contamination density is monitored using a 6200 Tencor Surfscan on the largest area. Using a 2 mm exclusion

Fig. 6. SOI structure after in-depth splitting.

Fig. 7. Schematic of the effect of hydrogen implantation into silicon a) without stiffener, b) with stiffener.

Fig. 8. Monitoring of the particle contamination density throughout the Smart-Cut process.

area, it is possible to detect particles responsible for specific defects on the edge of wafer bonding products. Figure 8 shows the evolution of the particle contamination

Fig. 9. Magic mirror view of the SOI structure obtained after splitting with standard cleaning.

Fig. 10. Magic mirror view of the SOI structure obtained after splitting with modified RCA cleaning.

density on both wafers throughout the process. Whereas the particle contamination density is very low on initial and oxidized wafers, implantation induces contamination and the density reaches 0.5 particles/cm<sup>2</sup>.

In the same way, the chemical state of the oxide surface was checked throughout the process using the contact angle measurement method with a water droplet placed on the surface. Results of measurement of the contact angle give an indication of the surface stress and of the hydrophilic state of the surface.<sup>13)</sup> Once again, the implantation step is responsible for most of the degradation of the hydrophilic state, the contact angle values increasing from 20–30° (on an oxidized wafer) to 50–65° (after implantation). This change is due to organic surface contaminants identified as hydrocarbons using MIR-FTIR spectroscopy.<sup>14)</sup>

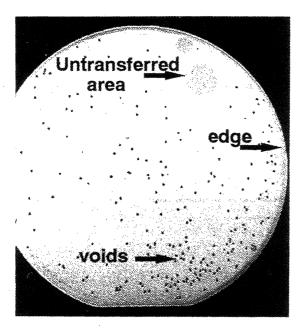

So, in the case of unoptimized cleaning, macroscopic defects can be detected just after the first annealing step, i.e, the splitting step (Fig. 9).

—Untransferred zones: large particles induce formation of an unbonded area, resulting in an effective local lack of stiffening effect, thus preventing the splitting from occurring in this area.

—Microvoids: particle and hydrocarbon contamination induces microvoid formation at the bonding interface. These small defects tend to inflate during annealing as soon as the splitting occurs, resulting in plastic deformation of the SOI surface.

—The bevelled edge of commercial wafers prevents bonding from occurring in a ring area about 1.5 mm wide and influences the adhesion over a few millimeters. This effect combined with particle contamination induces formation of the last type of macroscopic defect, small edge defects observed on SOI wafers.

All these defects are clearly visible by magic mirror view observation (Hologenix equipment).

For avoiing the formation of such defects, a specific

cleaning procedure using a modified RCA process was developed. After implantation, the bonding capability of the oxide surface is restored, almost no particle of a size larger than  $0.3\,\mu\mathrm{m}$  is trapped between the wafers at bonding, and the bonding site density (OH groups) is rather high, resulting in a high bonding wave velocity estimated to be in the range of 3–4 cm/s using IR transmission observation. This specific cleaning yields a final SOI structure free from macroscopic defects, as revealed by magic mirror view observation (Fig. 10).

# 4. Characterization of the SOI Structure

The SOI structure exhibits uniformity of the silicon layer thickness better than 10 nm min-max over 100 mm wafers. Surface microroughness is also a key parameter because of its impact on the gate oxide breakdown voltage. In addition to mean (1.2 Å) or RMS (1.5 Å) values, power spectral densities were investigated by AFM to check that Unibond wafers have a morphological surface structure quite similar to that of bulk silicon. 15)

For assessment of the crystalline quality of the silicon layer, chemical characterization was carried out using a four-step Secco etch. An etch pit density ranging from  $10^3$  to  $3\times 10^4/{\rm cm}^2$  was measured for 50 nm of silicon remaining after the first etch. SEM observations of the etch pits showed an unconventional shape for crystal defects. For checking of the density of crystalline defects, epitaxy was carried out on the SOI wafer. A Secco etch showed a very low defect density of about  $20~{\rm defects/cm}^2$ , identified as threading dislocations through the SOI layer. No stacking faults or slip lines were observed over wafers both before and after epitaxy demonstrating a very high crystal quality of the final SOI material. Moreover, a  $50\%~{\rm HF}$  solution etch for  $15~{\rm min}$  revealed an etch pit density of about  $1/{\rm cm}^2$ .

The electrical behavior of the SOI structure was evaluated using a pseudo-MOS transistor. <sup>16)</sup> Doping of the

silicon film is p-type and its concentration was measured as  $5 \times 10^{15}/\text{cm}^3$ . The interface state densities and mobilities were found to be as good as for the best SOI materials.

ULSI electronic devices made with ultra thin gate oxides  $(4\,\mathrm{nm})$  have demonstrated interesting electrical behavior. The breakdown intrinsic field was measured at about  $15\,\mathrm{MV/cm}$  on both SOI wafers and the best silicon materials. I-V measurements on capacitors of various sizes show that no pinhole or conductive defects exist in the buried oxide of the Unibond wafers.

# 5. Main Characteristics of the Smart-Cut Process and Advantages

#### 5.1 Layer thickness uniformity

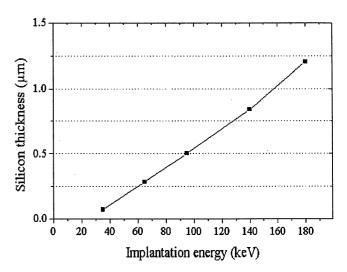

One of the benefits of the Smart-Cut process is the flexibility of the thicknesses of both the buried oxide and the silicon layers. The buried oxide layer is thermally grown and its thickness can be tuned with high reliability. The silicon upper layer of the SOI structure is obtained by splitting at the depth of maximum concentration of hydrogen  $(R_p)$ . The SOI structure thicknesses (Si thickness, SiO<sub>2</sub> thickness) are directly related to the ion energy through the relationship between the depth of maximum concentration of hydrogen  $(R_p)$  and implantation energy (rate of about  $8 \, \text{nm/keV}$  in silicon-Fig. 11), with no evidence of a dose effect.

The ion energy is accurately and easily controlled, so the layer thickness after splitting is inherently homogeneous (dispersion min-max <4 nm).

#### 5.2 Crystalline quality and interface quality

Using medium implantation doses and light ions minimizes atomic displacements giving rise to high crystalline quality SOI layers. Moreover, roughly one-half of the disturbed zone in the vicinity of  $R_{\rm p}$  is separated from the layer by the splitting process, and the other half is suppressed by the final polishing.

The Smart-Cut technology provides a very high-quality front interface (interface between the upper silicon layer and buried oxide). More precisely, the process is compatible with a front interface: silicon-thermally grown oxide, which guarantees the lowest interface state density. Due to the high penetration capacity of protons, it is possible to fabricate the buried dielectric layer through thermal oxidation at the very beginning of the process and then perform hydrogen implantation through this SiO<sub>2</sub> layer, even if it is rather thick. This is a great advantage when compared with the BESOI technology using etch-stop layers. In this case, keeping the etch-stop properties is hardly compatible with the thermal budget associated with the buried oxide thermal growth.

# 5.3 Industrial aspects

All the basic steps involved can be performed on standard microelectronics facility equipment. Implantation is performed on standard high-current machines designed for source-drain or polysilicon doping. Heat treatments can be performed in standard furnace tubes; cleaning is performed on wet-bench or wet cleaning machines de-

Fig. 11. Variation of the silicon layer thickness versus implantation energy for 400 nm thick oxide.

signed for ULSI technology, and in the last polishing step the same machines as for bulk wafer final polishing or chemical-mechanical polishing of inter-level dielectrics are used.

When compared with the SIMOX process, the Smart-Cut process presents the advantages of being based on a more "comfortable" and easier to industrialize process. Among the advantages, the following should be specially pointed out: for the Smart-Cut process the ratio of the dose range is up to fifty times less than that for SIMOX. Annealing treatments can be performed in classical furnaces instead of the specially designed very high temperature (1320°C) furnaces used for the SIMOX process.<sup>17)</sup>

Moreover, an additional economic advantage of the Smart-Cut process over BESOI technologies is apparent: no wafer is wasted in grinding operations and one SOI wafer is obtained for one bulk silicon wafer whereas in BESOI technologies two wafers are needed to obtain one SOI wafer.

#### 5.4 High potential

The principle of the Smart-Cut process is suitable for different kinds of applications:

—Single-crystal silicon films can be transferred onto any kind of substrate provided that this kind of substrate can be bonded to silicon and that the bonded structure can withstand temperatures in the 400°C–600°C range. Interesting results on single-crystal silicon on glass or quartz for display applications have been obtained.

—More generally, the principle of the Smart-Cut process applies to applications involving fabrication of single-crystal semiconductor films and their transfer onto different kinds of substrates. At LETI the process was applied successfully to silicon carbide<sup>18</sup> for making silicon carbide on insulator with a SiC monocrystalline layer 200 nm thick around 1000 nm of deposited oxide as insulator and either polycrystalline SiC or bulk silicon wafer as the underlying substrate. Other studies are planned for assessing the compatibility of the process with III–V semiconductors.

—The process also applies to transfer of structured and

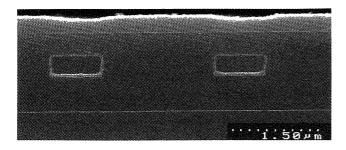

Fig. 12. SEM observation of the cross-section of the patterned film after transfer.

patterned layers<sup>19)</sup> or even transfer of electronic devices. The key issue for this kind of application is the compatibility of the process with non-homogeneous layers, i.e., the possibility of inducing continous splitting over the entire surface even if the microcavityes layer comprises discontinuous parts at different depths due to the structures of the various layers and the different compositions the proton beam encounters (Fig. 12). It was demonstrated that the process can be applied without any problem, provided that variations of the penetration depth remain lower than 100 nm: this is not a large constraint in the case of layers composed of SiO<sub>2</sub> patterns, Si patterns and Al patterns; all these materials exhibit similar behaviors with respect to ion penetration due to the similarities of their atomic number.

#### 6. Conclusion

The Smart-Cut process appears to be highly suitable for making high-quality SOI wafers with the great advantages, related to the intrinsic properties of light ion implantation, of low defect density and thickness homogeneity. All the basic steps involved can be performed on standard microelectronics equipment. The Smart-Cut process could be the way to fabrication of a less expensive but high-quality SOI material giving rise to rapidly increasing penetration of SOI technologies into the advanced mass production market.

# Acknowledgements

The authors wish to acknowledge H. Moriceau, C. Maleville, T. Poumeyrol, A. Soubie, A. M. Papon from LETI and T. Barge, F. Metral from SOITEC.

- A. J. Auberton-Hervé, J. M. Lamure, T. Barge, M. Bruel, B. Aspar and J. L. Pelloie: Semicond. Int. 11 (1995) 97.

- 2) J. P. Colinge: Proc. Int. Electron. Device Meet. (1994) p. 817.

- J. B. Lasky: Appl. Phys. Lett. 48 (1986) 78.

- 4) W. P. Maszara: Proc. Fourth Int. Symp. on Silicon on Insulator Technology and Devices, ed. D. N. Schmidt, Vol. 90-6, The Electrochem. Soc. Series, Pennington (1990) p. 199.

- P. M. Mumola, G. J. Gardopee, P. J. Clapis, C. B. Zarowin,

L. D. Bolliger and A. M. Ledger: Proc. 1992 IEEE Int. SOI

Conf., Florida (1992) p. 152.

- 6) Unibond is a registered trade mark of SOITEC.

- 7) M. Bruel: Electron. Lett. **31** (1995) 1201.

- M. Bruel: Nucl. Instrum. Methods Phys. Res. B 108 (1996) 313

- R. G. Saint Jacques: Nucl. Instrum. & Methods 209/210 (1983) 333.

- W. J. Choyke, R. B. Irwin, J. N. McGruer, J. R. Townsend, N. J. Doyle, B. O. Hall, J. A. Spitznagell and S. Wood: Nucl. Instrum. & Methods 209/210 (1983) 407.

- 11) S. K. DAS: Rad. Eff. 53 (1980) 257.

- 12) T. Abe and M. Nakano: Proc. Fourth Int. Symp. on Silicon on Insulator Technology and Devices, ed. D. N. Schmidt (The Electrochem. Soc., Pennington, 1990) The Electrochem. Soc. Series, Vol. 90-6, p. 61.

- Y. Bäcklund, K. Hermansson and L. Smith: Proc. Semiconductor Wafer Bonding: Physics and Applications I/ 1992, eds. U. Gösele et al. (The Electrochem. Soc., Pennington, 1992) The Electrochem. Soc. Vol. 92-7, p. 82.

- 14) C. Maleville, B. Aspar, T. Poumeyrol, H. Moriceau, M. Bruel, A. J. Auberton-Hervé, T. Barge and F. Metral: Proc. Seventh Int. Symp. on Silicon On Insulator Technology and Devices, eds. P. L. F. Hemment et al. (The Electrochem. Soc., Pennington, 1996) The Electrochem. Soc. Series, Vol. 96-3, p. 34.

- 15) B. Aspar, H. Moriceau and A. J. Auberton-Hervé: Proc. Seventh Int. Symp. on Silicon On Insulator Technology and Devices, eds. P. L. F. Hemment et al. The Electrochem. Soc., Pennington, 1996) The Electrochem. Soc. Series, Vol. 96-3, p. 99.

- 16) S. Cristoloveanu, A. Ionescu, C. Maleville, D. Munteanu, M. Gri, B. Aspar, M. Bruel and A. J. Auberton-Hervé: Proc. Seventh Int. Symp. on Silicon On Insulator Technology and Devices, eds. P. L. F. Hemment et al. (The Electrochem. Soc., Pennington, 1996) The Electrochem. Soc. Series, Vol. 96-3, p. 142.

- 17) J. Margail, J. M. Lamure, A. M. Papon: Proc. Fifth Int. Symp. on Silicon on Insulator Technology and Devices, ed. W. E. Bailey, (The Electrochem. Soc., Pennington, 1992) The Electrochem. Soc. Series, Vol. 92-13, p. 207.

- L. Di Cioccio, Y. Letiec, F. Letertre, C. Jaussaud and M. Bruel: Electron. Lett. 32 (1996) 1144.

- B. Aspar, M. Bruel, M. Zussy and A. M. Cartier: Electron. Lett. 32 (1996) 1985.