# **Device Reliability Report**

## Second Quarter 2014

UG116 (v10.1) August 7, 2014

## **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08/07/2014 | 10.1    | Changed many tables to show second quarter 2014 test data.  Chapter 1, The Reliability Program  Updated Table 1-16 and Table 1-17. Updated SEU and Soft Error Rate Measurements, page 26.  Chapter 2, Results by Product Family  Data was updated in many tables. The Autoclave Test section was removed for CPLDs. HASTU has substituted Autoclave for the reliability monitor program.  Chapter 3, Results by Package Type  Added packages for PQ160, PQ208, page 72 and FBG484, page 79.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 05/02/2014 | 10.0    | Changed many tables to show first quarter 2014 test data. Removed obsolete 0.22 µm Virtex® FPGA product data. Added package data for CLG400, FLG1926, FLG1928, and HCG1932. In Chapter 3, removed tables for packages CS280, CS484, FF1513, FF1517, PQ100, PQ160, PQ208, PQ240, CSG280, and PCG84. Added data for packages CLG400, FLG1926, FLG1928, and HCG1932. Added <i>Appendix A</i> , <i>Additional Resources and Legal Notices</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 03/18/2014 | 9.8     | Replaced reliability data for package FFG1928, page 100. Added reliability data for package FLG1925, page 101. Revised the Revision History section for readability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 02/14/2014 | 9.7     | Changed many tables to show fourth quarter, 2013 test data. Removed reliability data for the obsolete XCSxxxXL 0.25 µm device. Removed Spartan®-3 FPGA Autoclave data. HASTU has substituted Autoclave for the reliability monitor program.  Chapter 1, The Reliability Program  Updated Table 1-8 Product ESD and Latch-up Data, Table 1-15 ESD and Latch-up Data for 7 Series FPGAs and Zynq-7000 AP SoCs, Table 1-16 Summary of the Failure Rates, and Table 1-17 Real Time Soft Error Rates.  Chapter 2, Results by Product Family  Updated and moved existing tables. Updated test results in Temperature Cycling Test, page 41, High Accelerated Stress Test, page 46, Unbiased High Accelerated Stress Test, page 57. Updated test results in Temperature Cycling Test, page 62, Unbiased High Accelerated Stress Test, page 63, and Data Retention Bake Test, page 65.  Chapter 3, Results by Package Type |

|            |         | Alphabetized Non-Hermetic packages SO20, VO20, VO48, PC44, PC84, PC20, PQ100, PQ160, PQ208, PQ240, TQ100, TQ144, VQ44, VQ100, HQ208, and HQ240. Removed package BGG256 from Reliability Data for Pb-Free Packages, page 77.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/19/2013 | 9.6     | Changed many tables to show third quarter, 2013 test data. Removed reliability data for the obsolete XC95xxx 0.5 µm device. Removed Spartan-3 FPGA Autoclave data. HASTU has substituted Autoclave for the reliability monitor program.                                                                                                                                                                                                   |

|            |         | Chapter 1, The Reliability Program                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |         | Updated Table 1-7, Wafer Process Technology Family, Table 1-8, Product ESD and Latch-up Data, Table 1-15, ESD and Latch-up Data for 7 Series FPGAs and Zynq-7000 AP SoCs, Table 1-16, Summary of the Failure Rates, and Table 1-17, Real Time Soft Error Rates. Added devices XC7V2000T, XC7VH580T, XC7VX1140T, and XC7Z100 to Table 1-15.                                                                                                |

|            |         | Chapter 2, Results by Product Family                                                                                                                                                                                                                                                                                                                                                                                                      |

|            |         | Deleted the Autoclave Test section in Temperature Cycling Test, page 41.                                                                                                                                                                                                                                                                                                                                                                  |

|            |         | Chapter 3, Results by Package Type                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |         | Added packages BG352, BG432, BG560, page 67, FB676, page 68, FF484, FF784, page 68, FG320, page 70, FF896, FF900, FF901, page 69, BGG256, page 85, FBG900, page 79, FFG1513, FFG1517, page 81, FFG1696, FFG1704, FFG1738, FFG1759, FFG1760, FFG1761, page 81, FGG256, page 82, FLG1925, FLG1926, FLG1928, page 84, and FSG48, page 84.  Added FBG900, SBG484, FFG1928 and their plots to Board-Level Reliability Tests, Pb-Free, page 95. |

| Date       | Version | Revision                                                                                                                                                                                                                           |

|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08/16/2013 | 9.5     | Changed many tables to show second quarter, 2013 test data. Removed reliability data for the following obsolete devices:                                                                                                           |

|            |         | XC17(S)xxx/XL/E 0.6 μm                                                                                                                                                                                                             |

|            |         | XC4xxx/LE 0.5 μm                                                                                                                                                                                                                   |

|            |         | XC4xxxE 0.5 µm                                                                                                                                                                                                                     |

|            |         | XC4xxxXL 0.35 μm                                                                                                                                                                                                                   |

|            |         | XCSxxx 0.35 μm                                                                                                                                                                                                                     |

|            |         | XC4xxxXLA 0.25 μm                                                                                                                                                                                                                  |

|            |         | XC95xxxXV 0.25 μm                                                                                                                                                                                                                  |

|            |         | Chapter 1, The Reliability Program                                                                                                                                                                                                 |

|            |         | Updated Table 1-7, Wafer Process Technology Family, Table 1-8, Product ESD and Latch-up Data, Table 1-9, ESD and Latch-up Data for XC2VPxxx, Table 1-16, Summary of the Failure Rates, and Table 1-17, Real Time Soft Error Rates. |

|            |         | Added XC7VX980T to Table 1-15, ESD and Latch-up Data for 7 Series FPGAs and Zynq-7000 AP SoCs.                                                                                                                                     |

|            |         | Chapter 2, Results by Product Family                                                                                                                                                                                               |

|            |         | Deleted tables for obsolete devices. Updated data in many tables. Added Table 2-31, THB Test Results for Si Gate CMOS Device Type XC3SxxxA and Table 2-97, THB Test Results of Si Gate CMOS Device Type XC17SxxxA.                 |

|            |         | Chapter 3, Results by Package Type                                                                                                                                                                                                 |

|            |         | Deleted these tables:                                                                                                                                                                                                              |

|            |         | Table 3-24, Tests of Package Type DD8                                                                                                                                                                                              |

|            |         | Table 3-25, Tests of Package Type Chip Scale CC44                                                                                                                                                                                  |

|            |         | Table 3-61, Test Results of Device Types XC7VX485T, XC7VX690T under heading FFG1927.                                                                                                                                               |

|            |         | Deleted PG132 and PG175 from Table 3-27, Tests of Package Types PG84, PG120, PG156, PG191, PG223, PG299, and PG475. Deleted CB-100 and CB164 from and added CB196 to Table 3-28, Tests of Package Types CB196 and CB228.           |

|            |         | Updated data in many tables.                                                                                                                                                                                                       |

|            |         | Added package CS484, page 73. Added packages FF1924, FF1926, FF1927, FF1928, FF1929, and FF1930, page 70. Added packages FFG1924, FFG1926, FFG1926, FFG1927, FFG1928, and FFG1930, page 81.                                        |

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05/13/2013 | 9.4     | Changed many tables to show first quarter, 2013 test data.  Chapter 1, The Reliability Program  Added 7 series devices XC7VX330T, XC7VX415T, XC7VX550T, XC7VX690T and Zynq-7000 AP SoC devices XC7Z010, XC7Z030, and XC7Z045 to Table 1-15, ESD and Latch-up Data for 7 Series FPGAs and Zynq-7000 AP SoCs. Updated data for 0.25 μm, 0.35 μm, and 0.5 μm process technologies in Table 1-16, Summary of the Failure Rates. Updated data for 40 nm, 45 nm, and 28 nm technology nodes in Table 1-17, Real Time Soft Error Rates.  Chapter 2, Results by Product Family  Data in many tables was updated. Removed duplicate Table 2-17, HTOL Test Results for 0.15 μm Si Gate CMOS Device Type XCE2Vxxx. Deleted Table 2-69, Temperature Cycling Test Results for Si Gate CMOS Device Type XC4xxxXLA. Added Table 2-67, Temperature Cycling Test Results for Si Gate CMOS Device Type XCE4VxXxxx.  Chapter 3, Results by Package Type  Data in many tables was updated. Added packages FFG1923, FFG1924, FFG1925, FFG1926, FFG1927, FFG1928, FFG1929, FFG1930 and FFG1927 and |

| 04/02/2013 | 9.3     | their test results.  Changed many tables to show fourth quarter, 2012 test data. Added Xilinx 7 series FPGAs and Zynq-7000 All Programmable SoCs.  Chapter 1, The Reliability Program  Added XC7A100T, XC7A200T, XC7K70T, and XC7Z020 devices to Table 1-15 ESD and Latch-up Data for 7 Series FPGAs. Failure rate data changed in Table 1-16 Summary of the Failure Rates. Text and data changed in SEU and Soft Error Rate Measurements, page 26.  Chapter 2, Results by Product Family  Data in many tables was updated. Added Table 2-33 THB Test Results for Si                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            |         | Gate CMOS Device Type XCVxxx, Table 2-35 THB Test Results for Si Gate CMOS Device Type XC2Vxxx, Table 2-32 THB Test Results for Si Gate CMOS Device Type XC2SxxxE, Table 2-81 HAST Test Results for Si Gate CMOS Device Type XC4xxxE, and Table 2-104 HASTU Test Results for Si Gate CMOS Device Type XC4xxxLA.  Deleted Table 2-167, Summary of the Test Results for device XC2Cxxx/A from The TH test is conducted under the conditions of 85°C and 85% RH. Package preconditioning is performed on the testing samples prior to the TH test., page 61.  Chapter 3, Results by Package Type  Data in many tables was updated. Added packages CS144, CS324, CLG400, CLG484, FFG323, FFG324, FFG363 and their respective test results in Table 3-9 Test Results for Device Types XCV50, XC2V80, Table 3-11 Test Results for Device Types XC6SLX45, XC6SLX45T, Table 3-29 Test Results for Device Types XC2V1000, XC2V1500, and Table 3-49 Test Results of Device Types XC5VLX50.  Note: Table numbers are accurate as of the version 9.3 printing.                           |

| Date            | Version        | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date 02/12/2013 | Version<br>9.2 | Changed many tables to show the third quarter, 2012 test data. Added Xilinx 7 series FPGAs.  Chapter 1, The Reliability Program  Added XC7K160T, XC7K410T, XC7K420T, XC7K480T, XC7V585T, and XC7VX485T devices to Table 1-15, ESD and Latch-up Data for 7 Series FPGAs.  Chapter 2, Results by Product Family  Added Table 2-34, THB Test Results for Si Gate CMOS Device Type XCVxxxE, Table 2-95, HAST Test Results for Si Gate CMOS Device Type XCVxxxE, Table 2-103, HASTU Test Results for Si Gate CMOS Device Type XCVxxxE, Table 2-110, HASTU Test Results for Si Gate CMOS Device Type XCVxxxE, Table 2-111, HASTU Test Results for Si Gate CMOS Device Type XCVxxxE, Table 2-111, HASTU Test Results for Si Gate CMOS Device Type XCVxxxE                                     |

|                 |                | <ul> <li>(Shrink), Table 2-120, HASTU Test Results for Si Gate CMOS Device Type XCE4VxXxxx, Table 2-125, High-Temperature Storage Life Test Results of Si Gate CMOS Device Type XC4xxxXLA, Table 2-126, High-Temperature Storage Life Test Results of Si Gate CMOS Device Type XCSxxx, Table 2-141, High-Temperature Storage Life Test Results of Si Gate CMOS Device Type XCE4VxXxxx, and Table 2-160, Autoclave Test Results for Si Gate CMOS Device Type XCFxxxS/P.</li> <li>Chapter 3, Results by Package Type Added packages FF665, FF672, FF676, FFG665, FFG672, and FFG896. Added Table 3-47, Test Results of Device Types XC5VLX30T and Table 3-56, Test Results of Device Type XC2V1000.</li> <li>Note: Table numbers are accurate as of the version 9.2 printing.</li> </ul> |

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08/22/2012 | 9.1     | Changed many tables to show the second quarter, 2012 test data.  Chapter 1, The Reliability Program  Added entries for devices XC6SLX4 and XC6SLX9.  Removed obsolete reliability data for devices XC4VSX25, XC4VSX55, and XCV600E.  Chapter 2, Results by Product Family  Added entries for devices XC17S150A, XC3S250E, XC6VLX195T, XC7K410T, XC7VX485T, and XC9536.  Removed obsolete reliability data for the following devices: XC17(S)xxx, XC17(S)xxx(X)L, XC17(S)xxxE, XC1702L, XC17S15A, XC17S200A, XC17S50XL, XC17SxxxX, XC17SxxxXA, XC17SxxxXL, XC17Vxxx, XC18V01, XC18V02, XC18V04, XC18V512, XC18Vxxx, XC2C64, XC2S100E, XC2S150E, XC2V1500, XC2V3000, XC2VP100, XC2VP70, XC2VPxxx, XC2Vxxx, XC3S1000, XC3S100E, XC3S1400AN, XC3S200A, XC3SD1800A, XC3SDxxxA, XC3SxxxA, XC3SxxxAN, XC4013XLA, XC4VLX15, XC4VLX200, XC4VLX80, XC4VSX25, XC4VSX55, XC4xxxXLA, XC5VLX50T, XC6SLX150T, XC6SLX45, XC6SLX45T, XC6VLX130T, XC6VLX760, XC95144XL, XC95144XV, XC95288XV, XC95xxxXL, XC95xxxXV, XCF01S, XCF04S, XCF08P, XCF16P, XCF32P, XCFxxx, XCFxxxP, XCFxxxS, XCS20, XCS40XL, XCSxxx, XCSxxxXL, XCV1000E, XCV1600E, XCV400, XCV400E, XCV405E, XCV600E, XCV812E, XCVxxx (shrink), XCVxxxE, XCVxxxE (shrink)  Chapter 3, Results by Package Type  Added entries for devices XC7K410T and XC7VX485T.  Removed obsolete reliability data for the following devices: XC17256E, XC17S100A, XC17S100XL, XC17S200A, XC17S50A, XC18V01, XC2C128, XC2C256, XC2S300E, XC2VP100, XC2V250, XC2V500, XC2V6000, XC2V80, XC2VP100, XC2VP50, XC2VP100, XC3S1500, XC3S4000, XC3S5000, XC4085XLA, XC4VLX100, XC4VLX25, XC5215, XC5VLX50, XC6SLX150T, XC6SLX16, XC6SLX45, XC6SLX45, XC6SLX45T, XC6VLX130T, XC6VLX240T, XC6VLX475T, XC6VLX760, XC2VP50, XC9VLX475T, XC6VLX475T, XC6VLX475T, XC6VLX475T, XC6VLX475T, XC6VLX475T, XC6V |

| 05/08/2012 | 9.0     | Changed many tables to show the first quarter, 2012 test data. Added Xilinx 7 series FPGAs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 01/27/2012 | 8.1     | Updated Chapter 1, The Reliability Program Added XCE6VxXxxx to Table 1-7. Added XC5VSX240T to Table 1-12.  Chapter 2, Results by Product Family Added XCE6VxXxxx to Table 2-1. Deleted XC2S150 from Table 2-8. Added XCV100 to Table 2-9. Added XC6SLX45 and XC6SLX100 to and deleted XC6SLX16 from Table 2-23. Added XC4VLX160 and XC4VFX12 and modified Note 1 in Table 2-24. Added Note 1 to Table 2-25 and Table 2-26. Inserted new table: Table 2-29. Added XC5VLX85T to table Table 2-45. Added XC6VLX365T to Table 2-46. Added XCS20XL to and deleted XCS10XL from Table 2-71. Added XC3S200AN to Table 2-84. Added XC6SLX4 to Table 2-85. Added XC2S100E to and deleted XC2S400E from Table 2-93. Added XCS20XL and XCSxxxX to Table 2-105. Added XC6SLX4 and XC6SLX9 to Table 2-117. Deleted XCR3064XL from Table 2-178. Added XC2C64 to Table 2-194. Added XCR3128XL to Table 2-214. Added XC2C64 to Table 2-215.  Chapter 3, Results by Package Type Added HTS to Table 3-3 and Table 3-47. Added HAST to Table 3-56.  Note: Table numbers are accurate as of the version 8.1 printing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/07/2011 | 8.0     | Changed most tables to show the third quarter, 2011 test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            |         | Chapter 1, The Reliability Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            |         | Updated Acceptance Criteria and added note 3 to Table 1-3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|            |         | Chapter 2, Results by Product Family  Added XCV600E to Table 2-12. Added XC2VP7 to and deleted XC2VP80 from Table 2-15. Deleted XC3S2000 from Table 2-18. Deleted XC4VLX15 from Table 2-24. Added XC6VLX130T to Table 2-28. Added XC4VLX80 to Table 2-43. Added XC2V6000 to Table 2-77. Deleted XC4VFX100 and XC4VLX85T from Table 2-85. Added XC5VLX330T device to Table 2-86. Added XC6VLX195T device to Table 2-87. Added XC6SLX25T to Table 2-99. Added XCV100 to Table 2-123. Added XC6SLX16 to Table 2-136. Added XC4VLX80 to Table 2-137. Deleted XC17S150XL from Table 2-146. Deleted XCF128X from Table 2-148. Deleted XC17S30XL from Table 2-152. Deleted XCF01S, XCF04S, XCF08P, and XCF128X from Table 2-155. Deleted XC17S30XL from Table 2-163. Deleted XC17V16 from Table 2-164. Deleted XC17S30XL from Table 2-169. Deleted XC17V16 from Table 2-170. Deleted XCF01S, XCF04S, XCF08P, and XCF128X from Table 2-170. Deleted XC95216 from Table 2-174. Added XCR3256XL and deleted XCR384XL and XCR3512XL from Table 2-192. Added XCR3256XL and deleted XCR384XL and XCR3512XL from Table 2-201. Added XCR3256XL and deleted XCR384XL and XCR3512XL from Table 2-201. Added XCR3256XL and deleted XCR384XL and XCR3512XL from Table 2-213.  Chapter 3, Results by Package Type  Added HASTU to Table 3-11. Deleted HTS from Table 3-12. Deleted HASTU from Table 3-15. Deleted Temperature cycling -40 to +125°C row from |

|            |         | Table 3-26. Added HASTU to Table 3-29. Added HTS to Table 3-43. Added HAST to Table 3-47. Added Temperature cycling -55 to +125°C row and HTS to Table 3-49. Added HTS to Table 3-66. Added Temperature humidity 85°C, 85% RH with bias row to Table 3-74.  Note: Table numbers are accurate as of the version 8.0 printing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 08/02/2011 | 7.0     | Changed most tables to show the <b>second</b> quarter, 2011 test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 06/17/2011 | 6.0.1   | Revised last sentence in SEU and Soft Error Rate Measurements, page 26 for clarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 05/09/2011 | 6.0     | Changed most tables to show the first quarter, 2011 test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 02/01/2011 | 5.12    | Changed most tables to show the fourth quarter, 2010 test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11/01/2010 | 5.11    | Changed most tables to show the third quarter, 2010 test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 08/10/2010 | 5.10    | Changed most tables to show the second quarter, 2010 test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 05/04/2010 | 5.9     | Changed most tables to show the first quarter, 2010 test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 03/15/2010 | 5.8     | Changed most tables to show the fourth quarter, 2009 test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10/27/2009 | 5.7     | Updated most tables to include third quarter, 2009 test data. Added alpha particle FIT/Mb data for Spartan®-6 and Virtex®-6 FPGAs to Table 1-14, page 19.  Note: Table number is accurate as of the version 5.7 printing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 08/03/2009 | 5.6     | Changed most tables to show the second quarter, 2009 test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

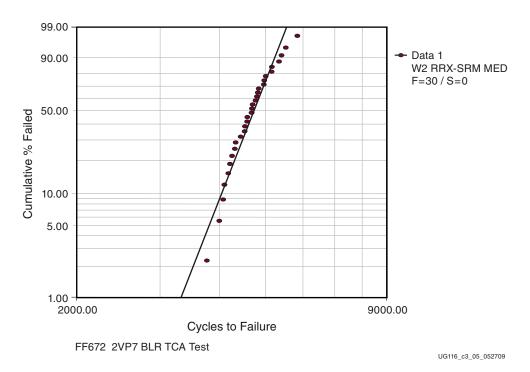

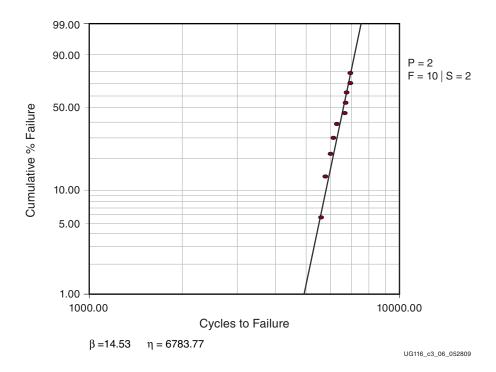

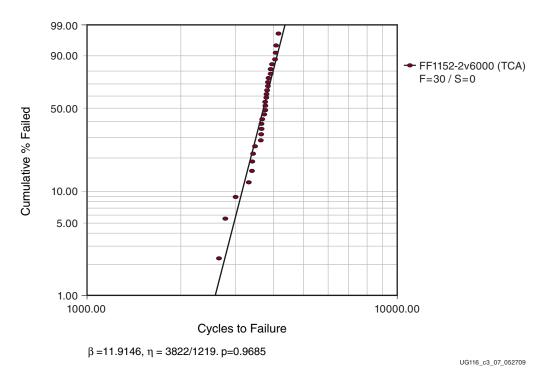

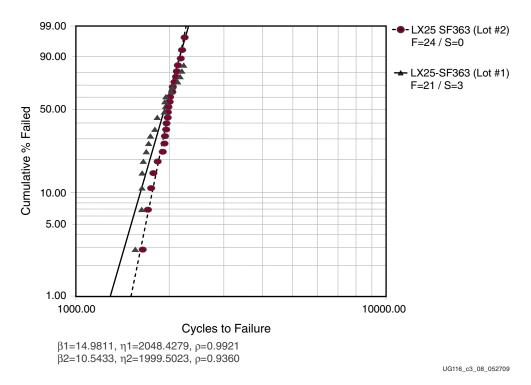

| 06/15/2009 | 5.5     | Added SF363 (Lot 2) data to Table 3-62, page 102. Replaced Figure 3-1, page 103, Figure 3-2, page 103, and Figure 3-3, page 104. Revised FFG1704 data in Table 3-64, page 108.  Note: Table and Figure numbers are accurate as of the version 5.5 printing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Date       | Version | Revision                                                                                                                                                 |

|------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05/07/2009 | 5.4     | Changed most tables to show the first quarter, 2009 test data. Added second paragraph to SEU and Soft Error Rate Measurements, page 26.                  |

| 02/11/2009 | 5.3     | Changed most tables to show the fourth quarter test data. Added single event upset and soft error rate data. See Table 1-14, page 19.                    |

|            |         | Note: Table number is accurate as of the version 5.3 printing.                                                                                           |

| 11/14/2008 | 5.2     | Changed most tables to show the third quarter test data. Updated legal disclaimer.                                                                       |

| 08/15/2008 | 5.1     | Changed most tables to show the second quarter test data.                                                                                                |

| 07/07/2008 | 5.0     | Changed most tables to show the first quarter test data.                                                                                                 |

| 02/06/2008 | 4.3     | Changed most tables to show the fourth quarter test data.                                                                                                |

| 10/31/2007 | 4.2     | Changed most tables to show the third quarter test data.                                                                                                 |

| 09/18/2007 | 4.1.1   | Corrected omission in this history table.                                                                                                                |

| 08/24/2007 | 4.1     | Changed most tables to show the second quarter test data.                                                                                                |

| 06/04/2007 | 4.0     | Changed most tables to show the first quarter test data.                                                                                                 |

| 03/28/2007 | 3.3.2   | Corrected typos in four tables.                                                                                                                          |

| 02/20/2007 | 3.3.1   | Corrected typos in three tables.                                                                                                                         |

| 02/12/2007 | 3.3     | Changed most tables to show the fourth quarter test data.                                                                                                |

| 12/01/2006 | 3.2     | Changed most tables to show the third quarter test data.                                                                                                 |

| 10/06/2006 | 3.1.2   | Corrected values in tables 1-12, 2-87, 2-90, and 2-91.                                                                                                   |

| 08/29/2006 | 3.1.1   | Changed typos in tables 2-91, 3-44, and 3-55.                                                                                                            |

| 08/11/2006 | 3.1     | Changed most tables to show the second quarter test data.                                                                                                |

| 06/20/2006 | 3.0.1   | Corrected two transposed figures in Table 1-10.                                                                                                          |

| 05/05/2006 | 3.0     | Changed most tables to show the first quarter test data.                                                                                                 |

| 02/24/2006 | 2.9     | Updated most tables to reflect the fourth quarter test data.                                                                                             |

| 11/17/2005 | 2.8     | Updated most tables to include the third quarter test data.                                                                                              |

| 08/19/2005 | 2.7     | Changed most tables to show the second quarter test values.                                                                                              |

| 05/20/2005 | 2.6     | Corrected data in tables 2-61 and 3-32.                                                                                                                  |

| 03/01/2005 | 2.5     | Changed most tables to show the fourth quarter test values. Removed packaging information from Chapter 1 and added a reference to the packaging website. |

| 01/04/2005 | 2.4     | Added third quarter data.                                                                                                                                |

| 08/18/2004 | 2.3     | Added second quarter data.                                                                                                                               |

| 05/24/2004 | 2.2     | Changed Tables 1-1, 2-1, 2-15, 3-44, 3-46, 3-48, 3-50, 3-52 and a heading on page 75.                                                                    |

| 05/24/2004 | 2.1     | Changed fit rate on page 7 for 0.5 µm from 89 to 8.                                                                                                      |

| 05/10/2004 | 2.0     | First quarter 2004 revision.                                                                                                                             |

| 02/09/2004 | 1.0     | Initial release in new template.                                                                                                                         |

## **Table of Contents**

| Revision History                            | 2    |

|---------------------------------------------|------|

| Chapter 1: The Reliability Program          |      |

| Overview                                    | . 14 |

| Product Qualification                       |      |

| Non-Hermetic and Hermetic Packages          |      |

| · ·                                         |      |

| Reliability Monitor Program                 |      |

| Process Technology Family                   |      |

| ESD and Latch-up Summary                    |      |

| Failure Rate Determination                  | . 25 |

| Failure Rate Summary                        | . 26 |

| SEU and Soft Error Rate Measurements        | . 26 |

|                                             |      |

| Chapter 2: Results by Product Family        |      |

| FPGA Products                               | . 28 |

| High-Temperature Operating Life (HTOL) Test |      |

| Summary                                     |      |

| Data                                        |      |

| Temperature Humidity with Bias Test         |      |

| Data                                        |      |

| Temperature Humidity Test                   | 39   |

| Summary                                     |      |

| Data Temperature Cycling Test               |      |

| Summary                                     |      |

| Data                                        |      |

| High Accelerated Stress Test                |      |

| Summary                                     |      |

| Unbiased High Accelerated Stress Test       |      |

| Summary                                     |      |

| Data                                        | 48   |

| High Temperature Storage Life               |      |

| SummaryData                                 |      |

| Flash PROM Products.                        |      |

| HTOL Test                                   |      |

| Summary                                     |      |

| Data                                        |      |

| Temperature Humidity with Bias Test                                    |    |

|------------------------------------------------------------------------|----|

| Summary                                                                |    |

| Data                                                                   |    |

| Temperature Humidity Test                                              |    |

| Summary                                                                |    |

| Data                                                                   |    |

| Temperature Cycling Tests                                              |    |

| Summary                                                                |    |

| Data                                                                   | 56 |

| Autoclave Test                                                         |    |

| Summary                                                                |    |

| Data                                                                   |    |

| Unbiased High Accelerated Stress Test                                  |    |

| Summary                                                                |    |

| Data                                                                   |    |

| Program/Erase Endurance Test                                           |    |

| Qualification Data                                                     |    |

| Data Retention Bake Test                                               | 58 |

| Summary                                                                | 58 |

| Data                                                                   | 59 |

| CPLD Products                                                          | 59 |

| HTOL Tests                                                             |    |

| Summary                                                                |    |

| Data                                                                   |    |

| Temperature Humidity with Bias Test                                    |    |

| Data                                                                   |    |

| Temperature Humidity Test                                              |    |

| Summary                                                                |    |

| Data                                                                   |    |

| Temperature Cycling Test                                               |    |

| Summary                                                                |    |

| Data                                                                   |    |

| Unbiased High Accelerated Stress Test                                  |    |

| Summary                                                                |    |

| Data                                                                   |    |

| Program/Erase Endurance Test                                           |    |

| Qualification Data                                                     |    |

| Data Retention Bake Test                                               |    |

| Summary                                                                |    |

| Data                                                                   |    |

|                                                                        |    |

| Chantar 2. Dagulta by Dagkara Typa                                     |    |

| Chapter 3: Results by Package Type                                     |    |

| Reliability Data for Non-Hermetic Packages                             | 67 |

| BG352, BG432, BG560                                                    |    |

| CP56                                                                   |    |

| CP132                                                                  |    |

| CS144                                                                  |    |

| CS324                                                                  |    |

|                                                                        |    |

| FB676                                                                  |    |

| FF484, FF784                                                           |    |

| FF665, FF668, FF672, FF676                                             |    |

| FF896, FF900, FF901                                                    |    |

| FF1136, FF1148, FF1152, FF1153, FF1154, FF1155, FF1156, FF1157, FF1158 |    |

| FF1696, FF1704, FF1738, FF1759, FF1760, FF1761                         | 69 |

| FF1923, FF1924, FF1925, FF1926, FF1927, FF1928, FF1929, FF1930                  | 70 |

|---------------------------------------------------------------------------------|----|

| FG256                                                                           | 70 |

| FG320                                                                           |    |

| FG324, FG456, FG484                                                             |    |

| FG676                                                                           |    |

| FS48                                                                            |    |

|                                                                                 |    |

| FT256                                                                           |    |

| PC44                                                                            |    |

| PD8                                                                             |    |

| PQ160, PQ208                                                                    |    |

| SF363                                                                           |    |

| SO20                                                                            | 73 |

| TQ100 TQ144                                                                     | 73 |

| VO20 and VO48                                                                   | 73 |

| VQ44, VQ100                                                                     | 74 |

| Reliability Data for Hermetic Packages                                          |    |

|                                                                                 |    |

| Reliability Data for PGA Packages                                               |    |

| Reliability Data for CB Packages                                                |    |

| Reliability Data for CF1144 Package                                             |    |

| Reliability Data for CG717 Package                                              |    |

| Reliability Data for Pb-Free Packages                                           | 77 |

| BGG352, BGG432, BGG560                                                          |    |

| CLG400, CLG484                                                                  |    |

| CPG132                                                                          |    |

| CPG196                                                                          |    |

| CSG144                                                                          |    |

| CSG324                                                                          |    |

| CSG484                                                                          |    |

| FBG484                                                                          |    |

| FBG676                                                                          |    |

| FBG900                                                                          |    |

| FFG323, FFG324, FFG363                                                          |    |

| FFG484, FFG784                                                                  |    |

| FFG665, FFG668, FFG672, FFG676                                                  |    |

| FFG896, FFG900, FFG901                                                          |    |

| FFG1136, FFG1148, FFG1152, FFG1153, FFG1154, FFG1155, FFG1156, FFG1157, FFG1158 |    |

|                                                                                 |    |

| FFG1513, FFG1517                                                                |    |

| FFG1696, FFG1704, FFG1738, FFG1759, FFG1760, FFG1761                            |    |

| FFG1923, FFG1924, FFG1925, FFG1926, FFG1927, FFG1928, FFG1929, FFG1930          |    |

| FGG256                                                                          |    |

| FGG320                                                                          |    |

| FGG324, FGG456, and FGG484                                                      |    |

| FGG400                                                                          |    |

| FGG676                                                                          |    |

| FGG900                                                                          |    |

| FHG1761                                                                         |    |

| FLG1925, FLG1926, FLG1928                                                       |    |

| FSG48                                                                           | 84 |

| FTG256                                                                          | 85 |

| HCG1155                                                                         | 85 |

| HCG1932                                                                         |    |

| PCG44                                                                           |    |

| PDG8                                                                            | 86 |

| PQG160, PQG208, PQG240                                                              | 86  |

|-------------------------------------------------------------------------------------|-----|

| QFG32, QFG48                                                                        | 87  |

| SFG363                                                                              | 87  |